1.2V SLVS Transceiver in UMC 110nm

A 200Mbps 1.2V SLVS transceiver solution.

Overview

A 200Mbps 1.2V SLVS transceiver solution.

This library delivers a compact and reliable 1.2V SLVS transceiver solution in UMC 110nm, optimized for high-speed, low-power applications. Featuring robust supply and ground noise rejection, 2kV HBM ESD protection, and integrated on die termination, this library provides both transmit and receive paths compliant with JESD8-13 SLVS standards at up to 200 Mbps. The library includes core SLVS cells alongside dedicated power, ground, and transition cells for seamless integration with foundry I/O. Post-layout simulations demonstrate excellent PSRR performance, clean eye diagrams across process corners, and stable operation from -40 C to 125 C. With flexible padring construction, bias sharing strategies, and detailed wire bond recommendations, UA11 ensures reliable integration into mixed foundry environments while minimizing area and power overhead.

Operating Conditions

| Parameter | Value |

| Devices | 1.2V Thin Oxides |

| BEOL | 1P7M2T |

| Core VDD | 1.2V |

| Tj | -40C to 150C |

| ESD | 2kV HBM, 500V CDM |

| Latchup | 200mA |

Cell Size

| Cell | Cell Size |

| SLVS | 112x80.8um |

| VDD | 56x80.8um |

| VSS | 56x80.8um |

| Transition | 5x80.8um |

Library Cell Summary

| Cell Type | Feature |

| SLVS | 1.2V 200MHz Transceiver |

| VDD | 1.2V Power |

| VSS | I/O and substrate ground |

| Transition | Transition cell |

Key features

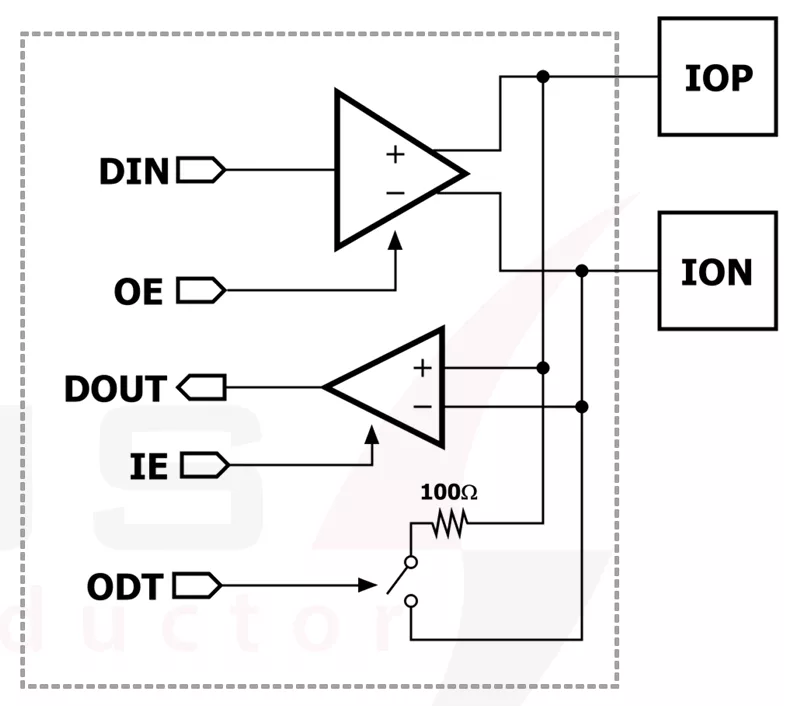

- High supply/ground noise rejection in both TX and RX.

- Small-area 2kV HBM protection.

- Input and output enable pins.

- Low-power bias strategy.

Block Diagram

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| UMC | 110nm | 110nm 1100 nm | — |

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about High-Speed IP core

PCIe 5.0: The universal high-speed interconnect for High Bandwidth and Low Latency Applications Design Challenges & Solutions

Understanding LTTPR: Enabling High-Speed DisplayPort Interconnects in Complex System Designs

Driving the Future of High-Speed Computing with PCIe 7.0 Innovation

High-Speed Test IO: Addressing High-Performance Data Transmission And Testing Needs For HPC & AI

eTopus attended TSMC 2025 Symposium and showcased high-speed interface IP solutions

Frequently asked questions about High-Speed I/O Pad IP

What is 1.2V SLVS Transceiver in UMC 110nm?

1.2V SLVS Transceiver in UMC 110nm is a High-Speed IP core from Certus Semiconductor listed on Semi IP Hub. It is listed with support for umc.

How should engineers evaluate this High-Speed?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this High-Speed IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.