Ultra-low power high dynamic range image sensor

Based on a time-domain pixel-level A/D conversion, its patented pixel architecture enables the capture of high dynamic range imag…

Overview

Based on a time-domain pixel-level A/D conversion, its patented pixel architecture enables the capture of high dynamic range images while consuming less than 1 mW for VGA resolution at 10 fps, a fraction of the power consumption of traditional image sensors.

Logarithmic data representation enables a 120 dB dynamic range coverage with 10-bit data words facilitating the analysis of visual scenes in real-world applications which naturally contain vastly changing environmental conditions.

Its in-pixel data memory relaxes data readout timing constraints thus enabling it to be used with microcontrollers with very limited data memory space. Moreover, its very low bill of material facilitates the integration in any system. This state-of-art image sensor makes autonomous vision systems powered by energy harvesting a reality.

On-chip memory

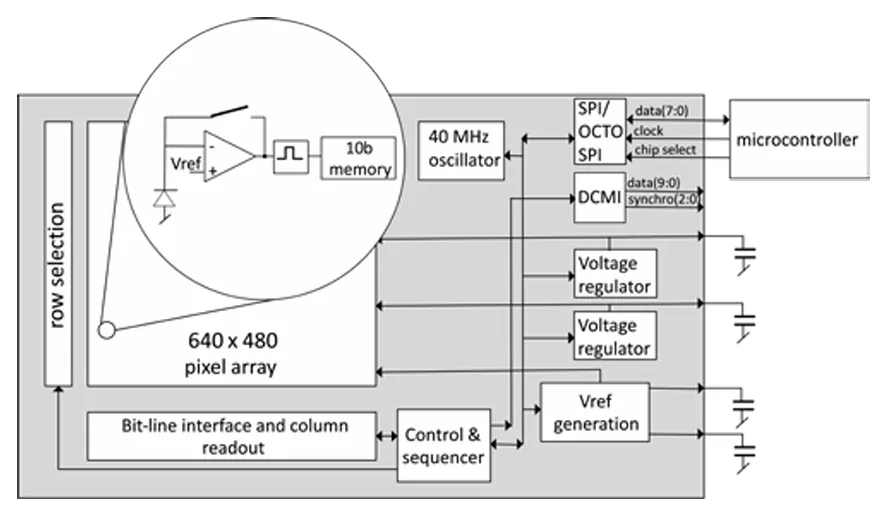

Each pixel incorporates a 10-bit static memory that serves two purposes:

- Together with an in-pixel comparator, it enables high dynamic range through continuous comparison of the voltage resulting from photocurrent integration with a reference level.

- As the digitized image is memorized on-chip, it can then be read out at a pace defined by the external device reading the image. This enables for example the use of microcontrollers with very limited memory, not able to store a whole frame.

Sub-sampling

A sub-sampled image can be read out to reduce the total amount of data transmitted for example for activity monitoring. As the whole image is still memorized on-chip, it can still be read out at full resolution or just a region of interest in case the analysis of the sub-sampled image led to the detection of activity.

Dual operation mode

In addition to its logarithmic high dynamic range mode, the ERGO640 can also be operated in linear mode like a standard imager to yield better image quality in low light conditions.

Ease of integration

The only external components needed are a few 1 μF capacitors. All pads are placed on a single side of the ERGO640 chip to enable a small footprint. Sensor control and data read out can be done through a standard 4-wire SPI if very limited communication interfaces are available, through an Octo-SPI bus, or combining a standard SPI for control and a 10-bit DCMI bus for data readout. The ERGO640 chip can be operated with a single 3.3 V supply, dual 3.3 V and 1.8 V supplies, or even single 1.8 V supply.

Key features

- Resolution: VGA (640 x 480)

- Backside illuminated sensor

- Pixel size: 6.3 μm x 6.3 μm

- Fill factor: 83 %

- Dynamic range: 120 dB intra-scene

- 10-bit data with logarithmic encoding

- On-chip frame memory

- Sub-sampling by 1/2, 1/4 and 1/8 for low power activity monitoring

- Region-of-interest readout

- Power consumption at 10 fps: 0.9 mW

- Supply voltage: 1.8 V and 3.3 V

- Active area: 4.03 mm x 3.02 mm

- Chip size: 4.4 mm x 4.9 mm

- SPI/OCTO-SPI interface for control

- Parallel interface (DCMI) or SPI/OCTO-SPI for data readout

Block Diagram

Applications

- Activity tracking

- IoT and wearable

- Code reading

- Biometry

- Retrofit meter reading

- Smart toys

- Animal monitoring

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Temperature Sensor IP core

Power Management for Internet of Things (IoT) System on a Chip (SoC) Development

Smart Transit Solution

High-Performance DSPs -> Voice control enhances appliance apps

Context Based Clock Gating Technique For Low Power Designs of IoT Applications - A DesignWare IP Case Study

Custom ASICs for Internet of Industrial Things (IoIT)

Frequently asked questions about Temperature Sensor IP cores

What is Ultra-low power high dynamic range image sensor?

Ultra-low power high dynamic range image sensor is a Temperature Sensor IP core from CSEM listed on Semi IP Hub.

How should engineers evaluate this Temperature Sensor?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Temperature Sensor IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.