BCH Encoder/Decoder IP Core

Nand Flash write cycles are limited.

Overview

Nand Flash write cycles are limited. An ECC detects and corrects failed operations, increasing the lifetime of the Nand Flash memory. For Nand Flash-based data storage, using an ECC is mandatory to ensure data validity. The powerful IPM-BCH is based on the BCH algorithm.

The BCH Encoder/Decoder is full-featured with multiple parameters to fit your own needs in FPGA and SoC designs. In fact IPM-BCH Encoder/Decoder is fully configurable, allowing to it reach the best latency or the smallest footprint.

Key features

- IPM-BCH for NandFlash Storage

- Up to 84 error-bits/block

- Configurable block size

- IPM-BCH for short code

- Option to be full asynchronous

- Option to be in 3 clock cycles

- Fully Configurable

- Latency

- Datapath

- Error number

- Packet size

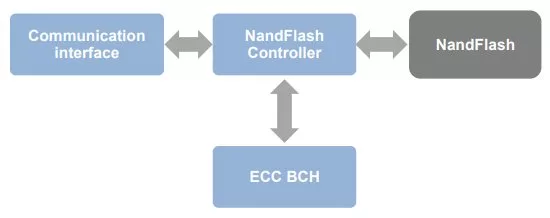

Block Diagram

Benefits

- Full hardware implementation for

- maximum performance, encoding,

- error detection and correction

- Balanced performance/gatecount

- All Galois fields covered

- Validated IP reduces Time-ToMarket

What’s Included?

- Verilog RTL source code.

- Synthesis scripts for Xilinx, Altera and Design Compiler.

- Technical documentation.

- Simulation testbench, with error injection.

- One year of maintenance and technical support.

- Supported simulators

- MTI Modelsim.

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Channel Coding IP core

Altera purchases optical network IP vendor Avalon Microelectronics

FAUST: On-Chip Distributed SoC Architecture for a 4G Baseband Modem Chipset

Satellite modems structure Internet access

Audio Transport in DisplayPort VIP

Extending the SoC Architecture of 3G terminal to Multimedia Applications

Frequently asked questions about Channel Coding IP cores

What is BCH Encoder/Decoder IP Core?

BCH Encoder/Decoder IP Core is a Channel Coding IP core from IP-Maker listed on Semi IP Hub.

How should engineers evaluate this Channel Coding?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Channel Coding IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.