16-bit Sigma Delta ADC

The IP is a 16-bit, delta-sigma (ΣΔ), analog-to-digital converter (ADC).

Overview

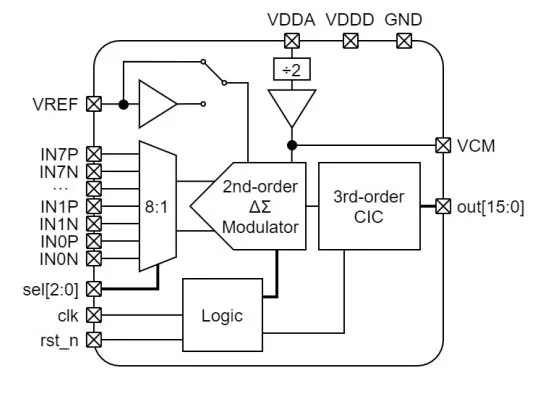

The IP is a 16-bit, delta-sigma (ΣΔ), analog-to-digital converter (ADC). It comprises of a second-order discrete-time modulator followed by a third-order CIC decimation filter with programmable output rate.

Two operation modes are supported: single differential input (free-running mode) or multiplexing of up to 8 differential channels (incremental mode).

The IP integrates a reference voltage buffer and common-mode generation. It requires an external clock of 8 MHz for 4 kSps data rate. A slower clock may be used to reduce power consumption.

The modulator area is 322 x 276 µm. It consumes 87 µA from a 1.2 V or 1.5 V supply. The decimation filter is synthesised to 898 cells, which take roughly 0.02 mm2.

This IP is implemented on GF130LP CMOS process using 8 metal layers and baseline mask set (i.e., no MIM capacitors or thin-film resistors). Please get in touch to enquire about migration to other processes.

Key features

- Dual operation mode:

- Single differential channel, free running

- 8 differential channels, incremental

- Programmable 3rd-order CIC output data rate:

- 90 dB SNR at 20 Sps output

- 12.5-bit ENOB at 4 kSps

- Low current consumption at maximum rate:

- 87 µA for the modulator

- Small footprint: 0.11 mm2 (including the CIC)

- May be supplied directly from cell battery:

- 1.20 V to 1.65 V analogue supply

- 1.20 V digital supply

- Optional 1 V reference buffer

- Optional 1 LSB dither injection

- Operating temperature: –40 °C to 85 °C

- Globalfoundries 130nm LP process

Block Diagram

Benefits

- Silicon proven

- Low power

- Small die area

Applications

- Sensing

- Industrial sensor interfaces

- Medical sensing

- Sports and healthcare wearable devices

- Battery/Low-power instrumentation

- On-chip monitoring

What’s Included?

- Datasheet

- Characterisation report

- Flat netlist (cdl)

- Decimation filter RTL code (SystemVerilog)

- Layout view of modulator (gds2)

- Synthesis constraints of decimation filter (sdc)

- Abstract view of modulator (lef)

- Behavioural model of complete ADC (Verilog)

- Timing view of complete ADC (lib)

- Integration guidelines and support

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| GlobalFoundries | 130nm | LP | Silicon Proven |

Specifications

Identity

Analog

Provider

Learn more about ADC IP core

Time Interleaving of Analog to Digital Converters: Calibration Techniques, Limitations & what to look in Time Interleaved ADC IP prior to licensing

Three ways of looking at a sigma-delta ADC device

Specifying a PLL Part 1: Calculating PLL Clock Spur Requirements from ADC or DAC SFDR

Save power in IoT SoCs by leveraging ADC characteristics

High Speed ADC Data Transfer

Frequently asked questions about ADC IP cores

What is 16-bit Sigma Delta ADC?

16-bit Sigma Delta ADC is a ADC IP core from EnSilica listed on Semi IP Hub. It is listed with support for globalfoundries Silicon Proven.

How should engineers evaluate this ADC?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this ADC IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.