High bit rate Turbo Decoder core for 3GPP LTE/ LTE A

The Lekha IP – 3GPP LTE Turbo Decoder IP Core V1.0 addresses the decoder implementation for the turbo coded transport channel com…

Overview

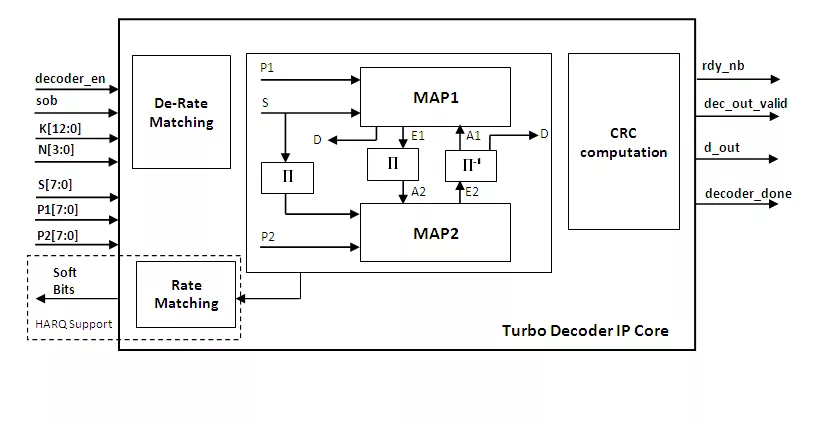

The Lekha IP – 3GPP LTE Turbo Decoder IP Core V1.0 addresses the decoder implementation for the turbo coded transport channel compliant to 3GPP TS 36.212 V 10.5.0. The Lekha Turbo Decoder IP is a highly parallel and hardware efficient architecture to meet high throughputs demanded by the LTE and LTE Advanced standards and next generation large MIMO systems. The decoder exploits algebraic properties of the quadratic permutation polynomial (QPP) interleaver, to avoid memory contention issues when several MAP decoders are used in parallel.

Key features

- 3GPP LTE/ LTE Advanced (LTE A) specification complaint

- Implements decoder for requirements as defined in Section 5.1.3.2 of the specification [1]

- Highly parallel and hardware efficient architecture

- Supports all code block sizes i.e., 40 – 6144

- Programmable number of iterations in half iteration step

- Support for Rate 1/3 coded output

- Programmable parallelism. Option for 1,2,4,8 MAP decoders in parallel.

- De-rate matching block can be optionally included

- Employs state metric propagation to improve performance of the decoder for high coding rates

- Easy interface definition.

- Customization to AXI or Avalon bus interface supported.

- Bit accurate C and MATLAB models available for RTL test vector generation.

- HARQ feature support

Block Diagram

Benefits

- High throughput rates are supported with this implementation and is easily customizable for area/ throughput tradeoffs.

- Supports CRC computation, HARQ feature support.

- The Lekha Turbo IP core alongwith few other functions is also available packaged as a bit rate co-processor. This solution helps system designers to either use this in conjunction with a DSP or in stand alone mode on a FPGA.

Applications

- Wireless Communications

- LTE/ LTE A UE Equipment

- Forward Error Correction blocks

What’s Included?

- Licensable in Netlist or Verilog or VHDL source format

- Target technology – Xilinx, Altera, Lattice devices

- Test bench

- MATLAB, C, VHDL, Verilog simulation models available

- Detailed technical documentation

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Channel Coding IP core

Altera purchases optical network IP vendor Avalon Microelectronics

FAUST: On-Chip Distributed SoC Architecture for a 4G Baseband Modem Chipset

Satellite modems structure Internet access

Audio Transport in DisplayPort VIP

Extending the SoC Architecture of 3G terminal to Multimedia Applications

Frequently asked questions about Channel Coding IP cores

What is High bit rate Turbo Decoder core for 3GPP LTE/ LTE A?

High bit rate Turbo Decoder core for 3GPP LTE/ LTE A is a Channel Coding IP core from Lekha Wireless Solutions Pvt. Ltd. listed on Semi IP Hub.

How should engineers evaluate this Channel Coding?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Channel Coding IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.