Overview

In channel coding redundancy is inserted in the transmitted information bit-stream. This redundant information is used in the decoder to eliminate the channel noise. The error correction capability of a FEC system strongly depends on the amount of redundancy as well as on the coding algorithm itself. The Low Density Parity Check (LDPC) codes are powerful, capacity-approaching channel codes and have exceptional error correction capabilities. The algorithm’s high degree of parallelism enables efficient, high-throughput hardware architectures.

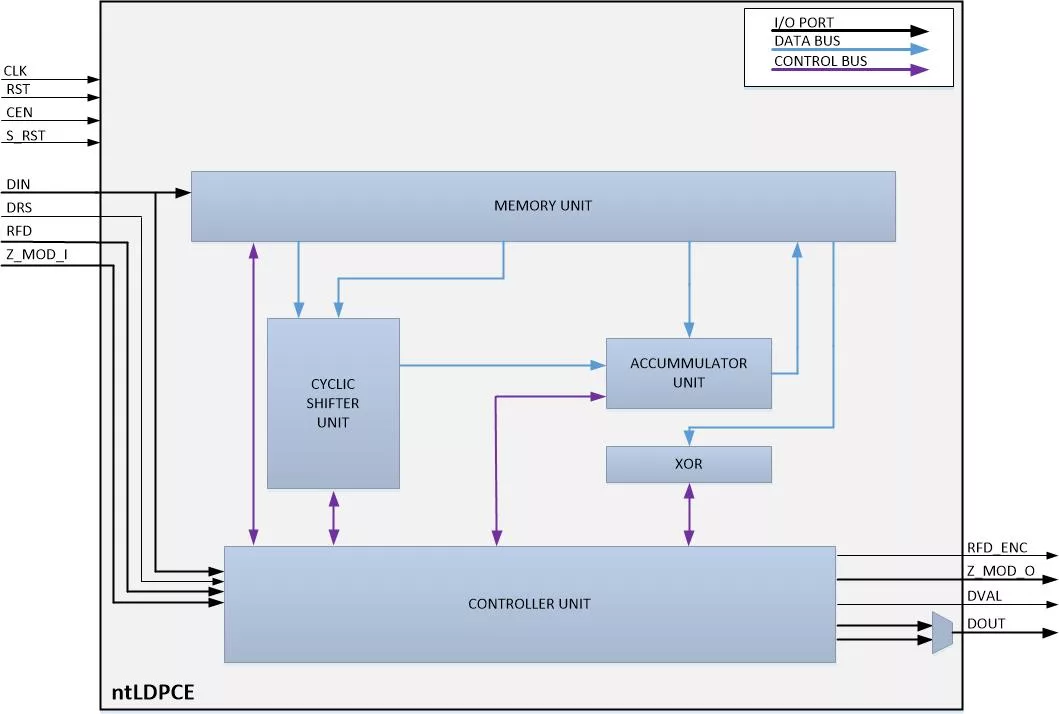

The ntLDPCE core implements the LDPC Block Codes (LDPC-BC). These LDPC codes are based on block-structured LDPC codes with circular block matrices. The entire parity check matrix can be partitioned into an array of block matri-ces, each block matrix is either a zero matrix or a right cyclic shift of an identity matrix. The parity check matrix designed in this way can be conveniently represented by a base (block) matrix. The main advantage is that they offer high throughput at low implementation complexity and they are used in many applications and communication standards.

The ntLDPCE core is fully configurable and compliant with various wireless and wireline communication standards including ITU-T G.9960 (G.hn), IEEE 802.16e (WiMAX), IEEE 802.11n/ac (WiFi) etc. Particularly, the core is highly reconfigurable and it is able to support different sub-matrix sizes (Z) of LDPC-BC, that are tailored for specific applications. It also supports varying on the fly code rates. The implementation is flexible, high speed, area optimized and has a simple interface for easy integration in SoC applications.

Learn more about Channel Coding IP core

This paper covers some practical aspects of designing the LDPC decoder starting from comparison between different techniques, different decoders parameters or standards, the effect of those parameters on the LDPC performance, also it discusses the algorithm selection process, and floating point implementation process.

We describe our SoC implementation of a baseband subsystem for a high performance 4G terminal. Our architecture, called FAUST, is based on distributed synchronization and asynchronous communication. We highlight how we have actually implemented these two

Satellite modems structure Internet access

DisplayPort uses Secondary Data Packets (SDPs), which are transported over the Main-Link that are not main video stream data. This allows it to carry audio and video simultaneously. The VIP supports audio transmission both in the original mode as defined in the specification as well as just as any other SDP being transmitted.

In this paper, a typical research case will be described on how to extend an existing SoC architecture of baseband processor on 3G terminal to the player on network multimedia compressed with MPEG-4, especially on how to build an effectively multi-layer a