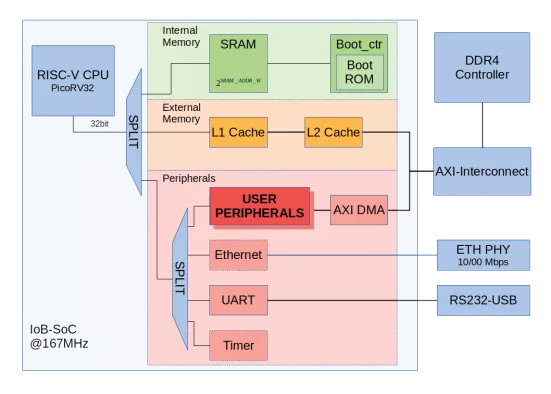

IOb-SoC is a RISC-V SoC template written in Verilog, which users can download for free, modify, simulate and implement in FPGA or ASIC. It supports stand-alone and booting modes, and can use internal RAM or an external DDR controller via L1/L2 cache systems.

RISC-V-based SoC template

Overview

Key Features

- Based on the picorv32 RISC-V CPU

- (Re)programmable via UART

- Runs from internal RAM or external AXI4 memory (DDR or other)

- L1 instruction and data caches

- UART

Benefits

- With IOb-SoC you can quickly and inexpensively build a complex embedded SoC

- Very small size and power consumption

Block Diagram

Applications

- All kinds of low-cost low-power embedded systems

Deliverables

- This IP can be downloaded for free from https://github.com/IObundle/iob-soc

- Premium features/services available on-demand:

- Higher performance CPU

- Custom hardware accelerators

- Custom peripherals

- Custom software

Technical Specifications

Foundry, Node

any

Maturity

FPGA-proven

Availability

Now