PCIe to UART bridge is a IP core which converts PCIe to UART bus interface

.

PCIe to UART Bridge

Overview

Key Features

- The following are the main features of the PCIe to UART Controller:

- System Interface.

- 100MHz external reference clock for synchronous clocking of PCI express Interface.

- Supports interface to external active low reset signal.

- PCI Express Interface.

- Compliant with the PCI Express base specification v1.1.

- Lane width supported x1.

- Link speed supported 2.5 Gbps.

- User interface width supported 32-bit.

- PCI Express Application Interface.

- Target only support.

- Memory BAR0 supported for UART controller.

- UART Interface.

- The UART bridge uses IO mapped interface.

- Full duplex asynchronous communication.

- Baud rate of 115200 with a single odd parity, stop & start bit.

- Supports transmit & receive synchronous FIFO of size 16 byte depth.

Benefits

- Compatible with different FPGA Vendors PCIe Hard IP.

- Configurable and ease of use in POS.

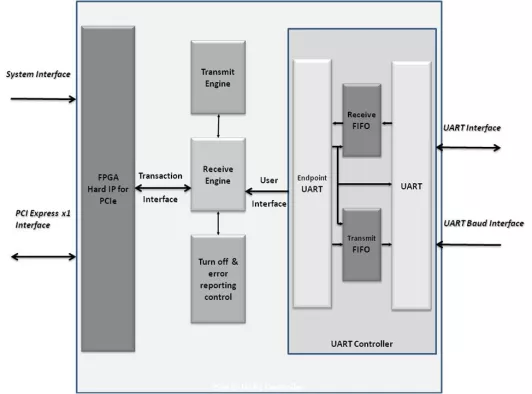

Block Diagram

Applications

- Used in POS

Technical Specifications

Maturity

Not Applicable.

Availability

Available

Related IPs

- A bridge to convert the slave SPI interface to the master UART interface and vice versa

- SPI to AXI4 Controller Bridge

- CMOS to MIPI CSI-2 Interface Bridge IP

- Four Input to One Output MIPI CSI-2 Camera Aggregator Bridge

- MIPI CSI-2 to CMOS Image Sensor Bridge

- MIPI DSI to OpenLDI LVDS Display Interface Bridge