PCI Controller

Overview

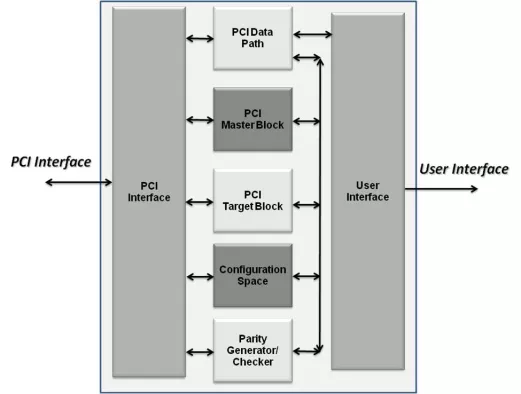

PCI Controller provides an interface between the PCI bus and user interface. PCI core interface is processor independent, enabling an efficient transition to future processor generations and use with multiple processors.

Key Features

- 64-bit, 33/66MHz PCI interface

- Supported initiator commands and functions:Parity generation, parity error detection

- Configurations read / write

- Memory read / write, memory read multiple, memory read line

- I/O read / write

- Interrupt acknowledge, special cycles

- Parity generation, parity error detection

- Master abort

- Supports a very generic user interface

- Supported target commands and functionsType 0 configuration space header

- Up to six base address registers.

- Memory read / write, memory read multiple, memory read line

- Target abort, target retry, target disconnect

- I/O read / write

- Medium speed DEVSEL timing

- Interrupt acknowledge

- PCI Configuration base registers are configurable from header file

Benefits

- Core enables concurrent operation of the local bus with the processor/memory sub system

- 64-bit extension doubles the bus bandwidth

Block Diagram

Applications

- Desktop and Departmental Servers

- Graphics and Multi-media Application

Technical Specifications

Maturity

Not Applicale.

Availability

Available.