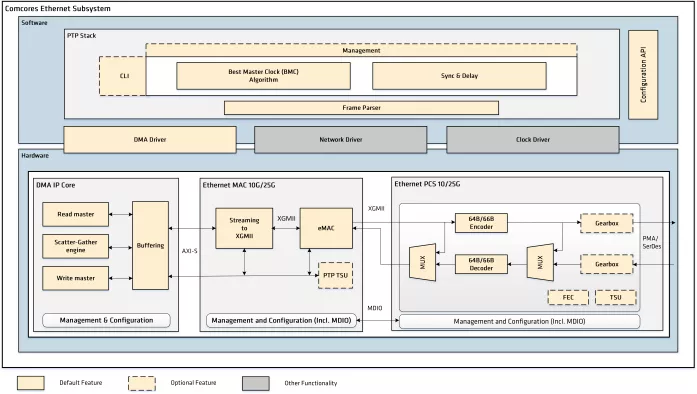

Comcores Ethernet Subsystem IP is a silicon-agnostic, easy-to-use integration of specific IP blocks. The subsystem IP is richly featured, highly configurable and comes in different variations of Ethernet MAC, Ethernet PCS, IEEE 1588 PTP (with Time Stamping Unit), DMA and can include TSN features.

The subsystem IP is ready for 5G applications, and is thoroughly tested and verified, thus reducing your risks and will save development time as the solution will reduce your design and integration efforts.

Ethernet Subsystem 10G/25G

Overview

Key Features

- Feature Rich

- FCS generation supported

- Deficit Idle Count for maximum data throughput supported

- Jumbo frames support

- Complete 10GBASE-R and 25GBASE-R PCS solution

- Configurable for several operating modes and speeds

- 64b 66b encoding/decoding

- Reconciliation Sublayer (RS) and 10 Gigabit Media Independent

- Interface (XGMII)

- Two-step messaging by default, with one-step messaging being optional

- Flexible

- The subsystem consists of various IP blocks that can be selected or deselected based on customers’ requirements. The main versions are:

- 01- Ethernet MAC and PCS

- 02- Ethernet MAC, PCS, and Timestamping Unit (TSU)

- 03- Ethernet MAC, PCS, and IEEE 1588 PTP (TSU and SW Stack)

- 04- Ethernet MAC, PCS, IEEE 1588 PTP (TSU and SW Stack), and DMA

- *** Ethernet MAC can be replaced by TSN MAC in all versions

- The subsystem consists of various IP blocks that can be selected or deselected based on customers’ requirements. The main versions are:

- 5G Ready

- The subsystem has been designed for 5G applications and has been delivered to 5G projects.

- Ease-to-use and Reliable

- HW validated subsystem

- IP blocks are integrated and tested together

- Silicon Agnostic

- Designed in VHDL and targeting both ASICs and FPGAs

Block Diagram

Deliverables

- The IP Core can be delivered in Source code or Encrypted format. The following deliverables will be provided with the IP Core license:

- Solid documentation, including User Manual and Release Note.

- Simulation Environment, including Simple Testbed, Test case, Test Script.

- Timing Constraints in Synopsys SDC format.

- Access to support system and direct support from Comcores Engineers.

- IEEE 1588 PTP SW

- DMA Driver

- Synopsys Lint and CDC

Technical Specifications

Maturity

Silicon proven

Availability

Available