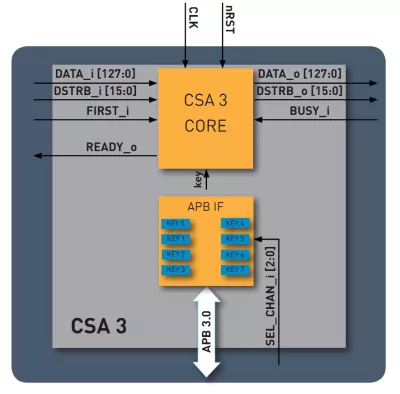

The CSA 3 descrambler IP core is hardware implementation of DVB Common Scrambling Algorithm version 3. It was designed to remove protection from scrambled broadcast data by flow-through decryption of transport stream. It has simple custom interface for data with flow control and APB 3.0 slave interface (backward compatible with APB 2.0) for set keys.

The CSA 3 descrambler IP core was designed for handled up to four different transport streams with even and odd keys for each TS. Handling of one 128-bit data word takes about 78 clock cycles (i.e. about 5 clock cycles per 1 byte).

CSA3 Descrambler

Overview

Key Features

- Full support of DVB CSA 3 Descrambling specification

- Flow-through architecture

- Up to 4 different transport streams

- APB 3.0 interface for programming

- About 100 K cells

Benefits

- Easy to integrate with standard APB interface and simple flow-through data interface

- High performance – about 5 cycles per byte

- Handling up to 4 different transport streams, even and odd keys for each

Block Diagram

Applications

- DVB set-top-boxes with conditional access support and multiple tuners

- Personal video recorders

- Conditional Access Modules

- Broadcast equipment

Deliverables

- RTL Source code

- Verification environment

- SDC for synthesis and STA

- User Guide

- Integration manual

Technical Specifications

Maturity

Pre-Silicon

Availability

NOW