Bring the best-in-class network connectivity to your hardware design with Enyx rock-solid and acclaimed Ethernet IP Cores. Minimize time-to-market with our full RTL implementation and support. Stay always at the forefront of technology with our frequent updates with the latest improvements and optimizations.

40G/25G/10G/1G TCP/IP + MAC

Overview

Key Features

- Management of layers 1, 2, 3 and 4 (OSI Model), compliant with

- Layer 1: Ethernet (IEEE802.3).

- Layer 2: Ethernet (IEEE802.3), ARP (RFC 826).

- Layer 3: IPv4 (RFC 791), ICMP (RFC 792) and IGMPv2 (RFC 2236).

- Layer 4: TCP (RFC 793), UDP (RFC 768) or UDP+PGM (RFC 3208).

- Layers 1 and 2: Physical and Data Link

- PHY Interface

- 1G – 10/100/1000M – 1000BASE-X/SGMII interface (9-bit @ 125 MHz) to integrated SGMII PHY or 1000BASE-X with PMA-PCS

- 10G – XGMII interface (72-bit @ 156.25 MHz) to integrated XAUI PHY or 10GBase-R with PMA-PCS

- 25G – XXVGMII interface (72-bit @ 390.625 MHz) to integrated XXVAUI or 25GBase-R with PMA-PCS.

- 40G – XLAUI interface (144-bit @ 312.5 MHz or 288-bit @ 156.25MHz)

- Raw MAC Stream Interface (access to MAC in promiscuous/transparent mode)

- 1G – 64-bit wide @ 125 MHz

- 10G – 64-bit wide @ 156.25 MHz

- 25G – 128-bit wide @ 195.3125 MHz

- 40G – 128-bit @ 312.5 Mhz or 256-bit@ 156.25 MHz

- Customizable MTU (Maximum Transmission Unit)

- Up to 9000 bytes payload to support from standard to jumbo frames.

- Layers 3 and 4: Network and Transport

- ICMP and ARP protocols

- Support for ARP static tables.

- Multiple Interfaces

- Up to 8 logical interfaces per instance, each of them with unique IPv4 and MAC addresses, VLAN ID, gateway and mask.

- Avalon/AXI-4 Streaming Interface

- 1G – 128-bit wide @ 125 MHz

- 10G – 128-bit wide @ 156.25 MHz

- 25G – 128-bit wide @ 195.3125 MHz

- 40G – 128-bit wide @ 312.5 MHz

- Configuration and management interface

- 32-bit Avalon-MM/AXI-4 lite slave control interface.

- Status and statistics available for monitoring at MAC, TCP and UDP session level.

- Linux Drivers and C API (Enyx Development Framework)

- With control, monitoring and streaming to/from CPUs.

- Support for non-offloaded protocols or sessions (DHCP, etc.)

- TCP/IP specifications

- Up to 32768 TCP simultaneous sessions per TCP instance.

- User configurable options for each session

- Configurable at runtime in client or server mode

- VLAN Priority, with insertion of PCP and DEI fields at emission.

- MSS.

- Window Scale Factor.

- Timestamp.

- Retransmission and reception buffers

- Customizable buffer size (depth and width)

- Internal or External memory support (DDRx, QDRx, …).

- Congestion Control

- Compliant with TCP New Reno algorithm.

- Computed for each session.

- Fast Retransmit

- Flow Control

- Sliding window mechanism.

- Packet reordering

Benefits

- 40G/25G/10G/1G Ethernet connectivity. Maximum bandwidth delivered with low latency.

- Full RTL Layers 2, 3 and 4, which include Enyx proprietary full-hardware TCP/IP, ARP, ICMP and MAC implementations.

- Easy to use standardized Avalon and AXI-4 interfaces.

- Multiple instances per FPGA and multiple logical interfaces per instance, each of them with a unique IPv4, MAC address, VLAN ID, Gateway and Mask.

- Up to 32768 TCP simultaneous sessions per instance, each of them configurable dynamically in server or client mode.

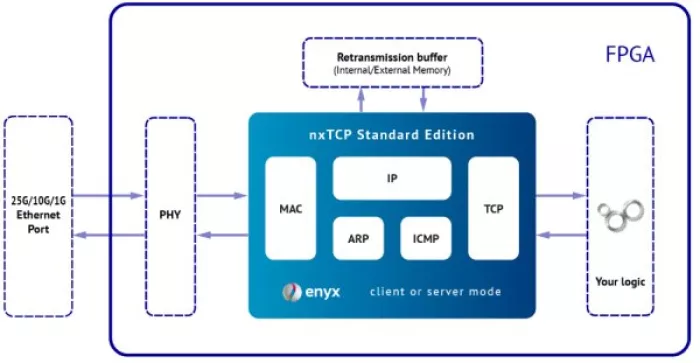

Block Diagram

Deliverables

- nxTCP IP Core

- Libraries for functional simulation

- Synthesizable VHDL and Verilog RTL (encrypted) for synthesis/implementation

- nxTCP Testbench

- Simulation libraries

- Client-Server Reference Designs

- Simulation environment and scripts

- Quartus II and Vivado Synthesis/implementation project for supported partner’s

- Integrated support for 10GBase-R or XAUI External PHY to QSFP/SFP+ module

- Complete Documentation

- nxTCP user’s manual

- Getting started guide

- Technical Support and Maintenance Updates

- 1 year of technical support

- 1 year of IP updates