The Chevin Technology 25GMAC IP core provides Ultra Low-Latency 25Gbit/s Ethernet connectivity in Xilinx Virtex® UltraScale™ FPGAs.

The 25GMAC can be integrated into customers’ products with an external or internal PCS, however we recommend using Chevin Technology’s 25GPCS for simplified integration and lowest possible latency.

25Gbit/s Ethernet MAC

Overview

Key Features

- Designed to IEEE 802.3 Specification

- Low Latency 20.5 ns

- Integrated FCS CRC32 check/generate

- Small Footprint, 2680 LUTs

- Flow Control option with Pause packets

- Programmable max frame length

- Reconciliation Layer -Local /Remote Faults

- Programmable Inter Frame Gap

- Deficit Idle Count for maximum throughput

- Cut-through mode for lowest latency

- Store-and-forward for minimum app load

- MAC address filtering options

- Detailed traffic analysis statistics collection

Benefits

- Exceptionally fast, reliable data transfer provides a competitive advantage

- Cost effective, high performance IP core

- Flexible licensing terms to suit customer requirements

- Integration support available if required

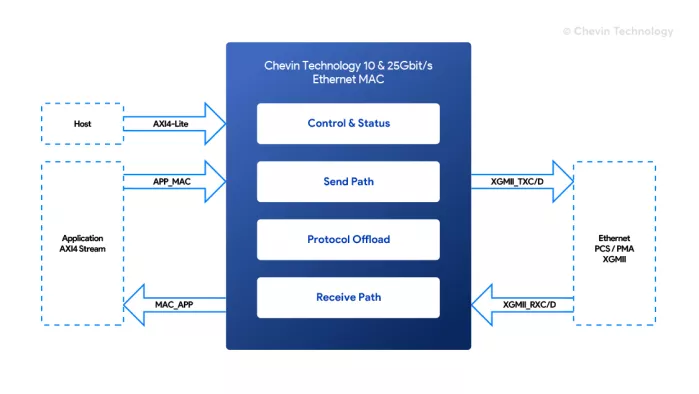

Block Diagram

Applications

- • Trade execution & monitoring

- • Science/ research

- • Data Storage & Capture systems

- • HPC / Big Data systems

- • Signal processing systems

- • Data Mining

Deliverables

- Encrypted RTL/VHDL source code

- Encrypted compiled netlist

- Datasheet & User Guide to assist integration

- Reference Design on Alpha-Data ADM-PCIE-8V3 board

- Simulation Test bench

- Build scripts for Vivado

Technical Specifications

Availability

Now